When configuring systems for multi-phase clocking – be it bi-phase for basic switched capacitor networks or many phases for sophisticated signal processing, it is often desirable for the clock phases to not overlap. As clock speeds increase, the rise and fall times of the individual phases need to squeeze within the “dead-time” allowed. Rise time being associated with bandwidth, the platform material may become a factor.

The inspiration for this discussion came about from an 8-phase clocking scheme developed for some prototype ADCs I once worked on. Getting the clocking scheme working as both desired and necessary turned out to be one of the more complex challenges of the project – everything works so well in the simulation universe – hence the discussion on rise times and non-overlap … keeping in mind that fall times are actually often slower than rise times.

I hope you enjoy the articles …

-

Clock Edges: Part 1 Introduction

In many mixed-mode circuits, various circuit functions may be controlled by multi-phase clocking. In many – if not most –

-

Clock Edges: Part 2 Harmonics

So, what to do, what to do … Let’s consider a system built on a printed circuit board (PCB). The

-

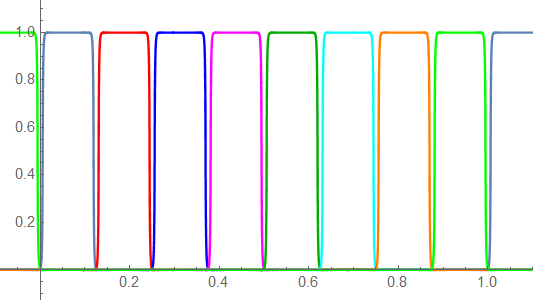

Clock Edges: Part 3 Non-Overlapping Clocks

The advent of multi-phase signal processing places greater constraints on what constitutes acceptable clocking criteria. The simplest case is a

-

Clock Edges Appendix

The Fourier Series for a finite sum may be defined as: where The coefficients are found to be: